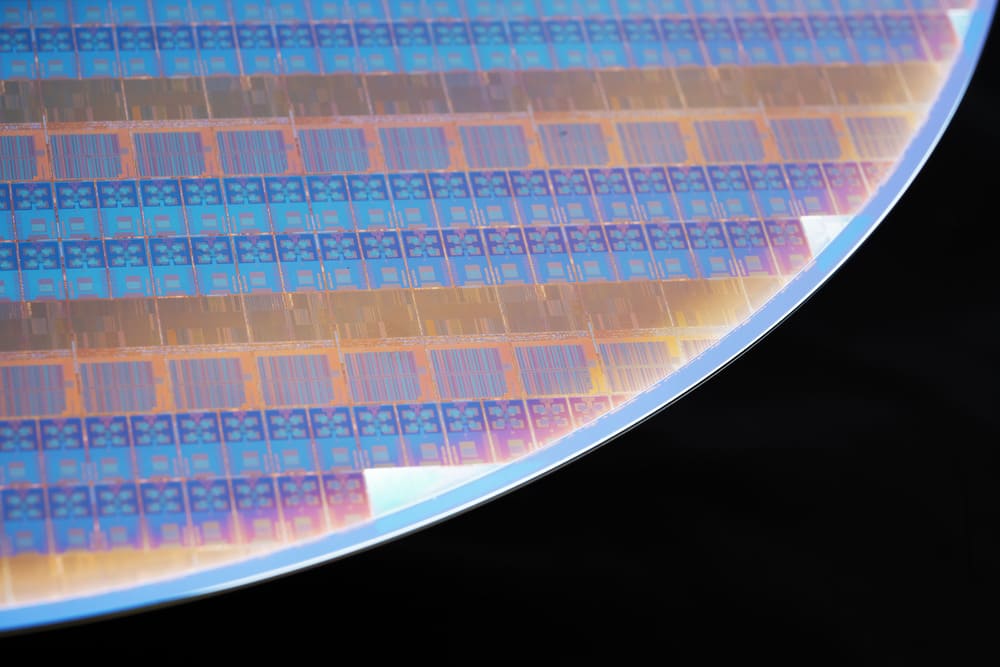

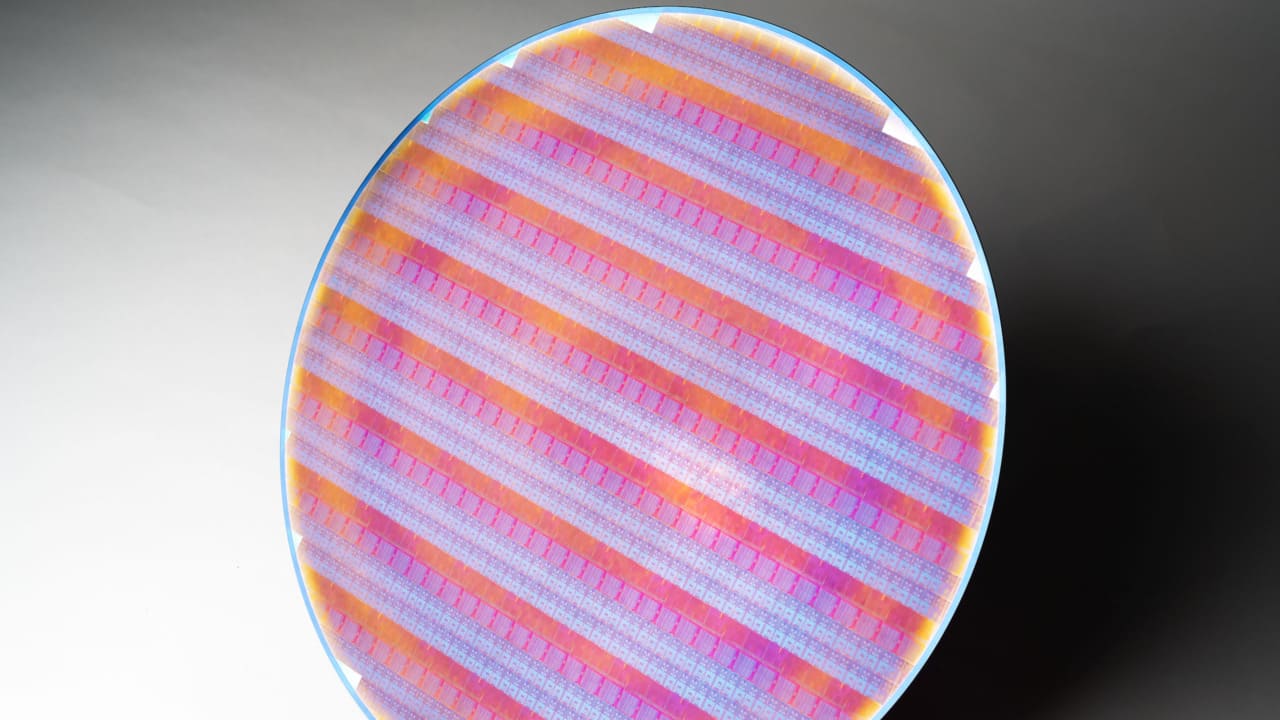

Intel is the first company in the sector a implement power from the back of a chip test with the same characteristics as the finished product. Thus obtaining a level of performance such as to project the world towards a new era of information technology. PowerVia, which will be deployed on the Intel 20A process node in the first half of 2024, is a leading rear-feeding solution. It solves the growing problem of area scaling interconnect bottlenecks by moving the feed path to the rear of the wafer.

Intel implements power from the back of the chip: how it works

Intel has decoupled the development of PowerVia from that of transistors to ensure that it was ready for implementation on node-based silicon processo Intel 20A e Intel 18A. PowerVia was tested on its own internal test node to debug and ensure good functionality of the technology prior to its integration into the Intel 20A with RibbonFET.

After fabrication and testing on a silicon test chip, PowerVia was confirmed to offer highly efficient utilization of chip resources, more than 90% of cells. But also an important scalability of transistor, enabling designers to achieve greater performance and efficiency in their products. Intel will present these findings at the VLSI Symposium from 11 to 16 June in Kyoto.

Intel implements power from the back of the chip thanks to PowerVia

PowerVia is far ahead of competitive rear-end power solutions. Offering chip designers, including Intel Foundry Services (IFS) customers, a faster path to major power and performance gains in their products. Intel has proven experience inintroduction of new technologies in the sector.

Choose Amazon Prime for your purchases, it’s free for 30 days

This is to advance Moore’s Law, such as strained silicon, Hi-K metal gate and FinFET. With the PowerVia and RibbonFET gate-all-around technology Coming in 2024, Intel continues to lead the industry in chip design and process innovations.

PowerVia is the first to solve the problem of bottlenecks in interconnections. An ever-increasing number of use cases, including AI and graphics, require smaller, denser, and more powerful transistors to meet their associated computational demands.

For decades now, the power and signal lines within a transistor architecture have used the same resources at the expense of one another. By separating the two, the chips can increase performance and energy efficiency and deliver better results. Rear-feeding is vital to reducing transistor size, allowing designers to increase transistor density without sacrificing resources to deliver more power and performance.

The technology introduced

Intel 20A e Intel 18A will introduce both PowerVia and rear-feed technology tecnologia Gate-all-around RibbonFET. As a completely new way of supplying power to transistors, the back-feed implementation has raised new challenges for heat dissipation and debugging.

By decoupling the development of PowerVia from the RibbonFET, Intel was able to quickly address these challenges to ensure readiness for implementation in silicon based on the 20A and 18A process nodes. Intel engineers have developed mitigation techniques to avoid overheating issues.

The debugging community also developed techniques to ensure that the new design framework could be properly debugged. As a result, the test implementation provided strong performance and reliability metrics while demonstrating the intrinsic value of the technology well before it joins the new RibbonFET architecture.

The test also made use of the design allowed by litografia EUV (Extreme Ultraviolet), which allowed for more than 90% standard cell utilization over large areas of the die, resulting in higher cell density which should translate into cost savings. The test also showed a more than 30% improvement in platform voltage drop and a 6% advantage in frequency. Intel also achieved thermal characteristics in the PowerVia test chip in line with the higher powers expected by logical scaling.

What will be the next developments?

In a third paper to be presented at the VLSI, the Intel technologist Mauro Kobrinsky will explain Intel’s research into more advanced ways of implementing PowerVia, including enabling signal and power on both the front and back of the wafer. Bringing PowerVia to market ahead of others in the industry while continuing to innovate is part of Intel’s long tradition of bringing constant advances to market.

Leave a Reply

View Comments